全球半導體產業在AI與高效能運算(HPC)的龐大需求下,正加速奔向後摩爾定律時代,不僅促使晶片架構從奈米級躍升至埃米級創新,也帶動先進封裝技術朝向系統整合與極致微縮發展。

在這個背景下,矽光子、HBM記憶體、晶背供電等先進製程的創新技術,正不斷改寫半導體產業的格局。

2024年9月,SEMI國際半導體產業協會宣布於SEMI平台上,由台積電與日月光號召, 從IC設計、製造封裝、應用模組至終端產品的企業及研究機構在內的半導體產業鏈,包括工研院、波若威、上詮、鴻海、聯發科、廣達到辛耘等 30多家企業及組織,共同成立SEMI矽光子產業聯盟。

目錄

什麼是矽光子?

矽光子就是用光來傳輸資料,並將其整合至矽晶片的技術,可供光學通訊、高速資料傳輸和光子感應裝置使用,由於可解決AI晶片頻寬大塞車的問題,是未來高速運算不可或缺的關鍵。

半導體基板物質是絕緣層上覆矽 (SOI) 晶圓,若使用標準半導體製程在矽的光子層上製造元件,而矽在紅外光下是透明的。

在矽周圍放置二氧化矽 (SiO2) 或空氣來產生高折射率差,可以使得在元件內傳播的光,於傳播通過電路時損耗極少。

晶片上的光子積體電路極小、耗電較低,運作速度也比傳統光子快,資訊傳輸比電子電路更快且效率更好。

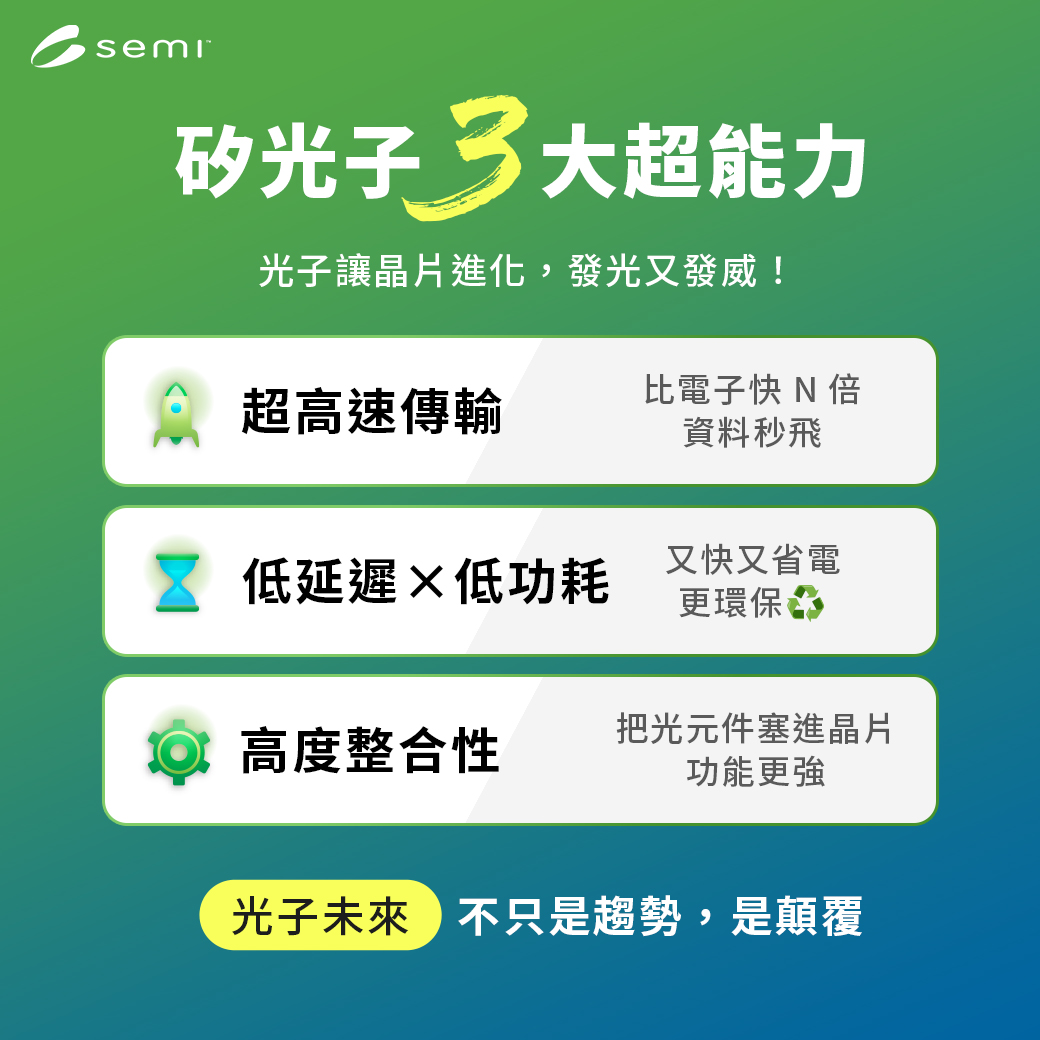

矽光子技術有哪些特點?

根據SEMI(國際半導體產業協會)說明,矽光子技術有三大特點。

第一, 從電走向光:隨著AI等新應用帶動大量運算需求,產業界將技術發展從電子訊號轉至具備高頻寬、低功率、傳輸距離更快的光訊號。

第二, 整合光波導元件:將光波導元件整合到矽晶片上,讓矽晶片同時處理電訊號的運算、光訊號的傳輸,就稱做矽光子。

第三, CPO(共同封裝光學技術)縮短傳輸途徑:過去模組會讓電子進到伺服器尾端的光收發器後,才轉成光;CPO讓電子直接進入訊號轉換處,變成光子,同時提升效能、降低功耗。

矽光子技術有哪些應用?

矽光子在半導體產業的第一波浪潮,是2017年應用於光纖網路及接受器等,透過ASIC(特殊應用積體電路)和矽光子共同封裝在基板上,大約可節省三成耗電。

第二波浪潮則是2022年與光學 I/O整合,透過ASIC 和 SiPh 共同封裝在Interposer上,大約可節省五成耗電。

日月光半導體執行長吳田玉曾表示,在半導體進入先進製程後,矽光子第三波浪潮可望應用在3D封裝,屆時有可能提升10倍資料傳輸頻寬、晶片厚度可望降低5倍,滿足汽車光達、行動裝置、感測器等領域等用途。

矽光子技術發展有什麼挑戰?

第一,矽光子積體電路需要將光耦合器、調變器、轉阻放大器等多種光學元件,整合在同一基板上。

然而,現階段矽光子多半應用在利基型市場,晶片代工廠都是客製化,各種光通元件類型的規格、封裝製程、材料沒有統一的規範與標準,因此需要一個整合包含 IC 設計、晶圓代工、封裝模組以及光電廠商等各次產業資訊的研發平台,才能達到更好綜效。

第二,矽光子技術有高速、體積小、低能耗等優勢,但開發與整合需要同時融合電子學與光學原理,因此還需要投入許多資金、人力、時間等研發成本,才能讓矽光子中的電子、光學元件才能彼此相容並持久穩定。

台灣產業對於矽光子有什麼布局?

前台積電董事長劉德音於美國加州大學柏克萊分校攻讀博士,博士論文題目就與矽光子技術相關。

他在加入台積電前,於1987~1993年服務於美國科技業知名的貝爾實驗室,擔任高速電子研究實驗室研究經理,研究主題也是現今備受關注的光通訊系統。

矽光子在國內半導體產業討論已久,台積電首次公開提到,是在2022年。

台積在2024年4月的北美技術論壇中指出,正研發緊湊型通用光子引擎(COUPE™)技術,以支援AI熱潮帶來的數據傳輸爆炸性成長。COUPE使用SoIC-X晶片堆疊技術將電子裸晶堆疊在光子裸晶之上,相較於傳統的堆疊方式,能夠為裸晶對裸晶介面提供最低的電阻及更高的能源效率。

當時台積電預計於2025年完成支援小型插拔式連接器的COUPE驗證,並於2026年整合CoWoS封裝成為共同封裝光學元件(Co-Packaged Optics, CPO),將光連結直接導入封裝中。

2025年1月,輝達執行長黃仁勳會見台積電董事長魏哲家後,接受媒體採訪時表示,輝達正與「全球最大的矽光子代工晶片製造商」合作,但他坦誠不太可能很快有結果,雙方仍需要數年時間才能也具體成果。

本文不授權媒體夥伴

延伸閱讀:

黃仁勳矽光子概念股出爐,台積電、矽品、鴻海、波若威入列!「這技術超棒,我們跟TSMC合作好一段時間了」

_20260102153424_20260325230950.jpg_1140x855_280x210.jpg)